An adapted BIOS saves power in existing designs

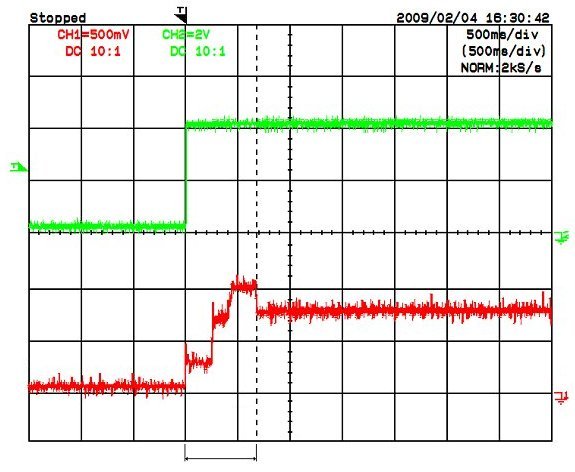

The picture shows the course of events when the H6036 exits STR through the GPIO port (green graph) being pulled high. At first, hardware voltage is switched on and stabilizes in 260 ms. Power consumption is increased (red graph) to a higher level when the embedded BIOS executes without cache memory. The processor runs slowly for about 200 ms prior to the cache memory being switched on. The maximum power consumption is reached when the chipset has set up the memory and the embedded BIOS executes at full speed. The start-up sequence (marked with arrows), from the point when the GPIO port is pulled high to a fully functional system, with a 7.0 W power consumption, is 680 ms long.

The picture shows the course of events when the H6036 enters STR through the GPIO port (green graph) being pulled low. At first power consumption (red graph) is increased when the embedded BIOS executes code handling SMI. The stop procedure (marked with arrows) brings the system to enter STR in 22 ms and decreases power consumption from 7.0 W to 0.7 W. 0.7 W is the power consumed in RAM and selected parts in the chipset.